0

0

0

0

0

0

0

Page 61

Page 91

ASIC-DESIGN MANAGERS FACE GLOBAL CHALLENGES

FORMAL TECHNIQUES

SOLIDIFY POWER-GRID VERIFICATION Page 71

**QUIET-NODE CURRENT**

SENSING TAMES NOISE

MAINTAINING CHANNEL COMPLIANCE IN HIGH-

**PROBLEMS** Page 81

SPEED BACKPLANES

0

0

**PCI EXPRESS**

ROLE Page 50

CLICK HERE TO RENEW

**CONTENDS FOR**

**COMMUNICATIONS**

0

0

0

0

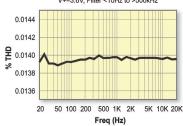

# Pure Power Cool Sound

# 300W, 110dB, 95% Efficient Audio Power Stage

The TAS5261, the newest offering in TI's PurePath Digital<sup>TM</sup> product line, is the highest power single-chip Class D power stage and delivers 110dB SNR for ultimate sound clarity and performance in home audio applications. It drives >300W into a  $4\Omega$  speaker (10%THD+N) with 95% efficiency for cooler operation and can drive 125W,  $8\Omega$  (THD+N<0.09%).

High Performance. Analog. Texas Instruments.

For datasheet, samples and evaluation module visit:

www.ti.com/tas5261

Technology for Innovators and the red/black banner are trademarks of Texas Instruments. 1674A0 © 2006 TI

Over 625,000 products from more than 320 quality name-brand manufacturers

Quality Electronic Components, Superior Service

1.800.344.4539 • www.digikey.com

\* New Product Added Daily!

# **Ancient Methods of Protection Will Only Take You So Far.**

When it comes to thwarting 21st century evildoers, nobody has more industry-proven secure IC solutions than Atmel®.

With a broad portfolio of biometric sensors, embedded security chips, RF identification chips, secure microcontrollers and secure memories for smart cards, and RFID/card readers, Atmel has the expertise and flexibility to provide customer-driven solutions for security in an unsecured world.

And, when it comes to measuring why we're good, don't just take our word for it. Our secure microcontroller product portfolio meets the stringent needs of the security market with some of the highest security certifications in the industry, including Common Criteria EAL4+/EAL5+, FIPS-140-2 Level 3 and 4, ZKA, Visa® International and MasterCard CAST approvals.

So, when your next project calls for security, think Atmel. We're Everywhere You Are®... securely.

Secure Memory and Microcontrollers for Smart Cards

**Smart Card Reader ICs**

Biometrics

Trusted Platform Module IC

**Embedded Security**

RF Identification

Check out Atmel's security solutions today at www.atmel.com/ad/securitysolutions

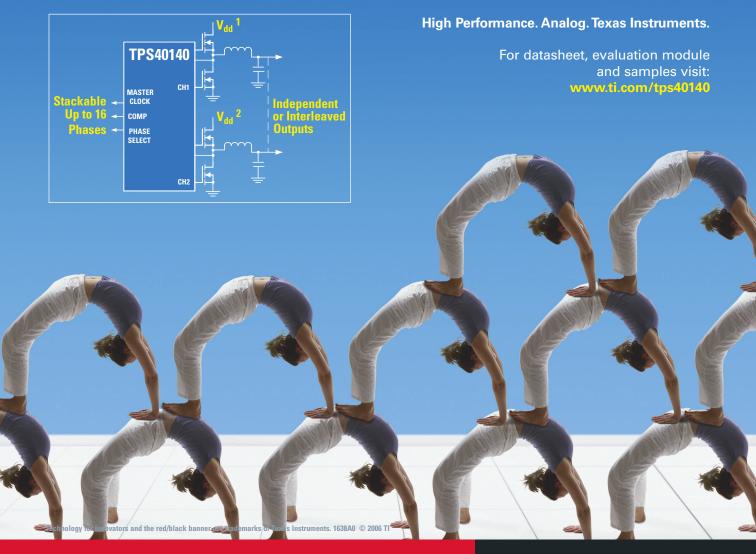

# Stackable. Scalable. Flexible. DC/DC Controller Boosts Efficiency

The TPS40140 turns power supplies in data center and telecommunication equipment into fully scalable, stackable power systems with greater load-handling capability and maximum efficiency. This unique PWM buck controller offers the simplicity of a stand-alone dual or two-phase controller with the ability to "stack" multiple devices together, creating a high-density power supply. Generating from 10 A to 320 A of output current, true interleaved operation enables maximum efficiency up to 16 phases.

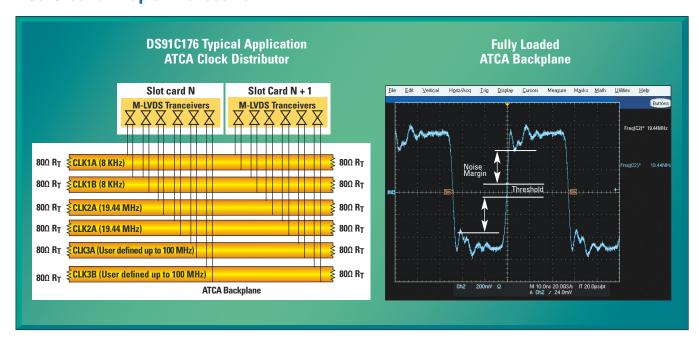

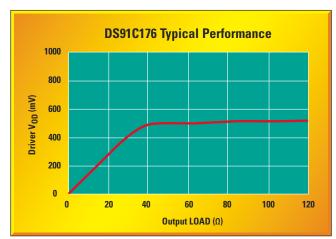

# **Boost Your Noise Margin with M-LVDS**

Drive as Many as 32 Loads with the DS91C176 Multipoint LVDS Transceiver and DS91C180 Full Duplex Transceiver

#### **Features**

- ullet Increases noise margin with controlled edges and constant  $V_{\mbox{OD}}$

- Controlled edges (2 ns typical) minimize backplane reflections and ringing

- Intelligent driver maintains constant output voltage keeping noise margins high

Ideal for use in all multi-drop backplanes, servers, basestations, storage, routers, cable driving, test and measurement, Advanced Telecom Computing Architecture (ATCA) platforms, and LXI instrumentation

For FREE samples, datasheets, and more information on the DS91C176/180, contact us today at:

lvds.national.com

Or call 1-800-272-9959

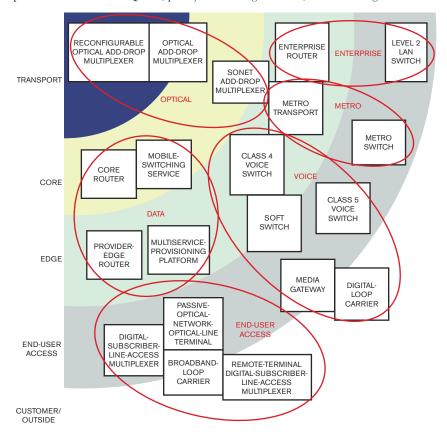

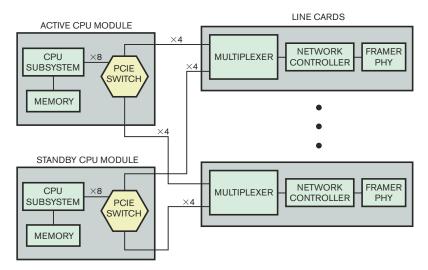

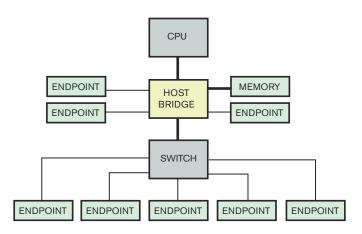

#### PCI Express contends for communications role

Scalable performance and low cost are making PCI Express attractive for communications-device designs, challenging proprietary-bus structures for next-generation design wins. by Richard A Quinnell, Contributing Technical Editor

#### **DLNA and HANA: two** visions of consumer multimedia networking

Consumers want painless networking and interoperability of multimedia devices. Here, two standards groups paint sometimes-conflicting pictures of how to achieve that goal-and how far such sharing should extend.

> by Matthew Miller, Executive Editor Online

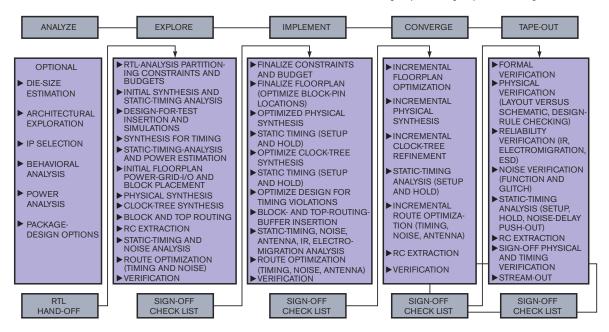

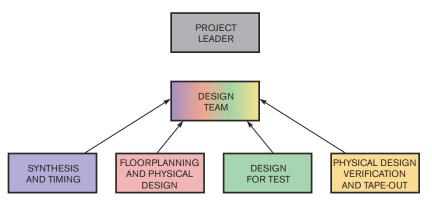

#### **ASIC-design** managers face global challenges

With resources and new business stretched across the globe, design managers are employing a range of methods to get designs done on time.

> by Michael Santarini, Senior Editor

# contents

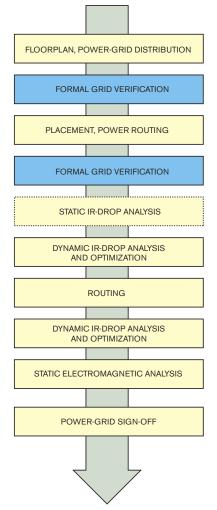

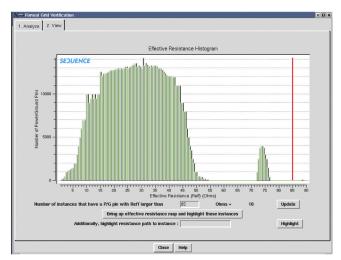

#### Formal techniques solidify power-grid verification

Formal grid verification provides an opportunity for users to sign off on the structural integrity of the power grid before proceeding to voltage-drop and electromigration by Ersin Beyret, analysis. Sequence Design Inc

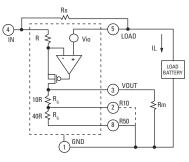

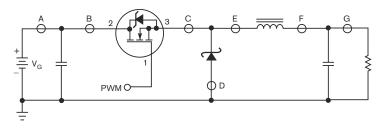

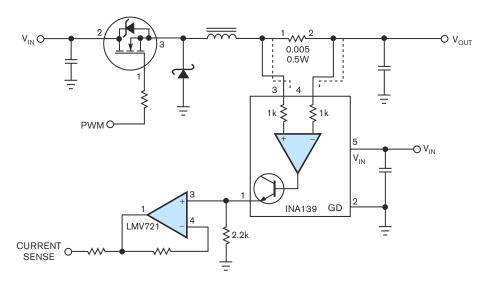

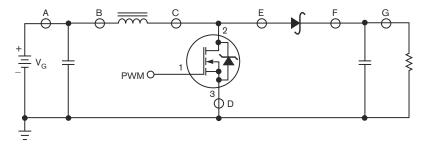

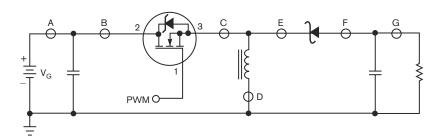

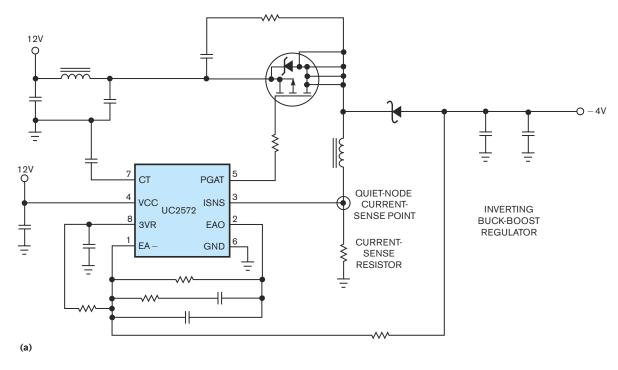

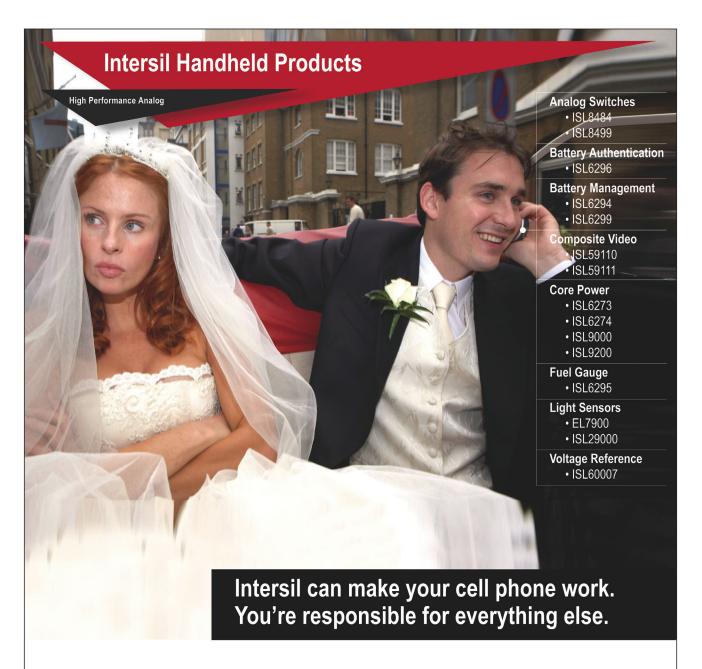

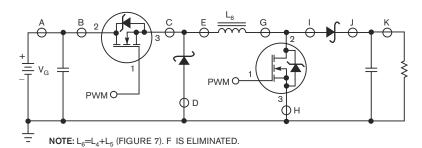

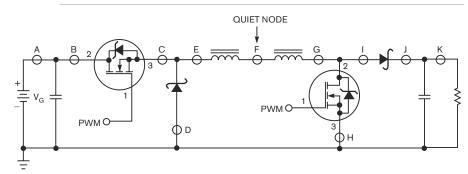

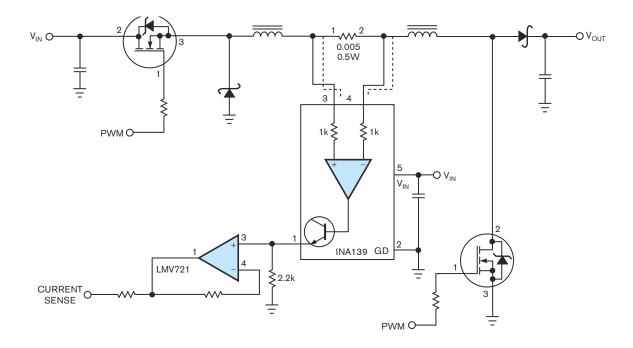

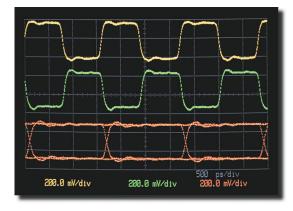

#### Quiet-node current sensing tames noise problems

Where you locate the current-sense resistor in your dc/dc converter can have a profound effect on the device's performance.

> by Claude Abraham, Bendix Commercial Vehicle Systems

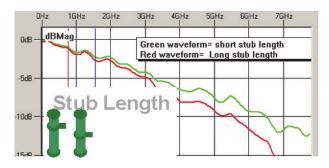

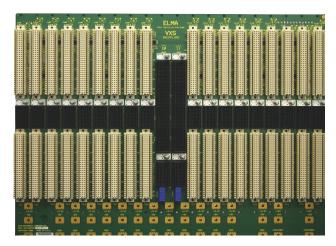

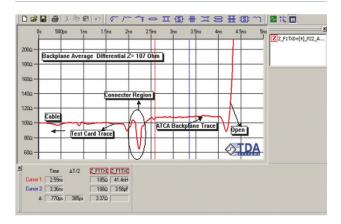

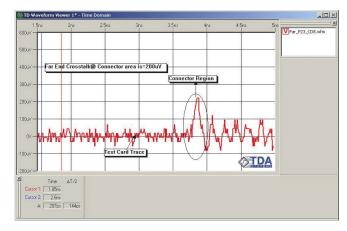

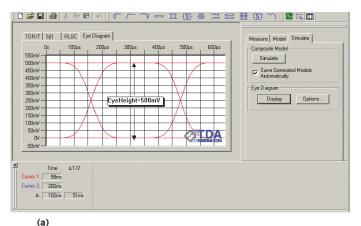

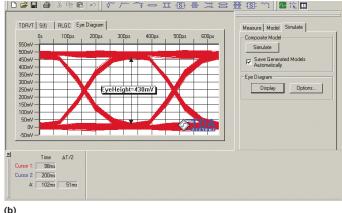

#### Maintaining channel compliance in highspeed backplanes

As speeds increase across the backplane, it becomes more challenging to maintain high signal quality. The role of design engineering for backplanes is evolving. by Bogdan Gavril, Elma Bustronic

# ESIGNIDEAS

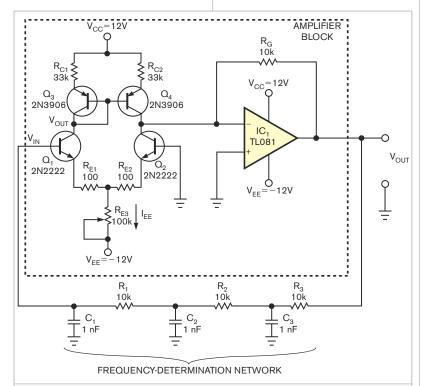

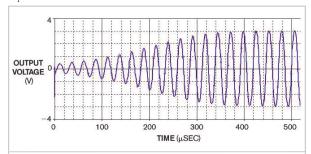

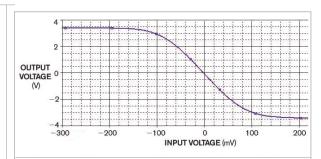

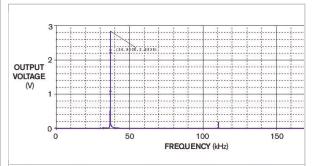

- Soft limiter for oscillator circuits uses emitter-degenerated differential pair

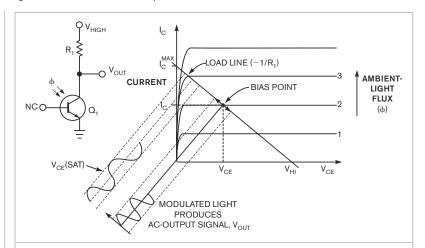

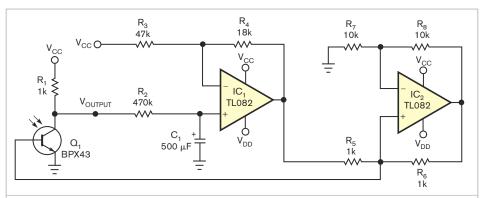

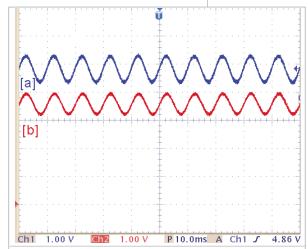

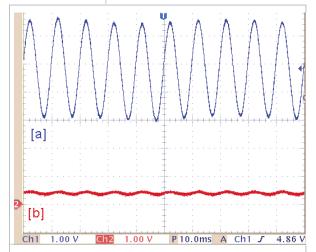

- 100 Feedback circuit enhances phototransistor's linear operation

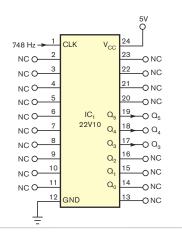

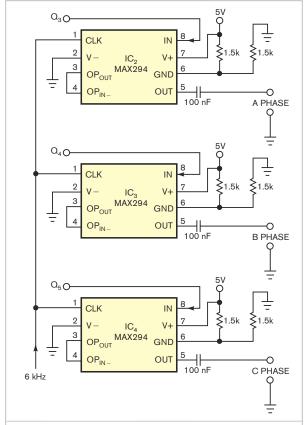

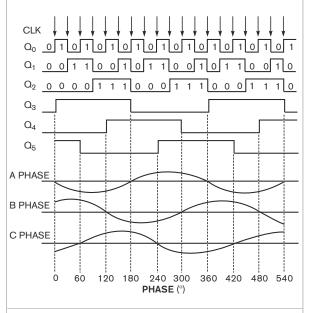

- 104 Three-phase sinusoidal-waveform generator uses PLD

- Send your Design Ideas to edndesignideas@reedbusiness.com.

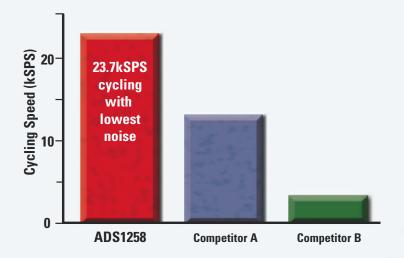

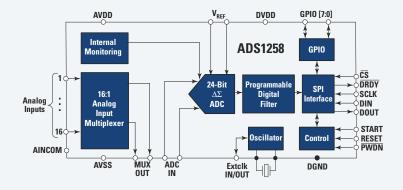

# **Fastest Cycling 24-Bit ADC**

The **ADS1258** 16-channel, 24-bit ADC from Texas Instruments features the lowest latency, fastest channel cycle rate and lowest noise of any competitive devices. With a measurement latency of 42 $\mu$ s, the ADS1258 can measure all of its 16 input channels in less than 675 $\mu$ s with only 12 $\mu$ Vrms of input referred noise, offering unmatched performance for precision, multi-channel data acquisition applications.

Evaluation Modules

Available Today

www.ti.com/ads1258 ° 800.477.8924, ext. 13497

### **contents** 10.12.06

- 7.1-GHz, low-phase-noise spectrum analyzer costs \$11,995

- Tool generates HDLs directly from Simulink

- 55-nm embedded-DRAM process debuts

- Test products support PCI Express, HDMI

- "Lite" version of IP interconnects hardware blocks

- Downconverter simplifies wideband applications

- 26 Research Update: 1.5-nm organic cell encapsulates memory; Laser on a chip targets terabit rates; Mechanism interlocks nano-oscillators

- Global Designer: Develop software early on virtual ARM hardware; 3G subscriptions to reach 285 million worldwide by year-end

## DEPARTMENTS & COLUMNS

- 12 EDN.comment: Triple-play trickery: Beware the buzzword bandwagon

- 32 Milestones That Mattered: Monolithic op amps: A lab tool became indispensable

- 38 Signal Integrity: Frequent obsession

- 40 Tales from the Cube: Sidebands be gone, or let there be (no) light

- 118 **Scope:** Looking at the ATCA Summit, private equity companies, and solar cells

# ROUNDU

- 111 Discrete Semiconductors: High-voltage ICs, power MOSFETs, SuperFET devices, and more

- 113 Microprocessors: Dual-core processors, 650-nApower-consumption microcontrollers, development kits, and more

EDN® (ISSN#0012-7515), (GST#123397457, R.B.I. Intl Pub Mail #0280844) is published biweekly, 26 times per year, by Reed Business Information, 8878 Barrons Blvd, Highlands Ranch, CO 80129-2345. Reed Business Information, a division of Reed Elsevier Inc, is located at 360 Park Avenue South, New York, NY 10010. Tad Smith, Chief Executive Officer, Stephen Moylan, President, Boston Division. Periodicals postage paid at Littleton, CO 80126 and additional mailing offices. Circulation records are maintained at Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Telephone (303) 470-4445. POSTMASTER: Send address changes to EDN®, PO Box 7500, Highlands Ranch, CO 80163-7500. EDN® copyright 2006 by Reed Elsevier Inc. Rates for nonqualified subscriptions, including all issues: US, \$165 one year, Canada, \$226 one year, (includes 7% GST, GST#123397457); Mexico, \$215 one year; air expedited, \$398 one year. Except for special issues where price changes are indicated, single copies are available for \$10 US and \$15 foreign. Publications Mail Agreement No. 40685520. Return undeliverable Canadian addresses to: Deutsche Post, 4960-2 Walker Road, Windsor ON N9A 6J3. E-mail: subsmail@reedbusiness.com. Please address all subscription mail to EDN®, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. EDN® is a registered trademark of Reed Elsevier Properties Inc, used under license. A Reed Business Information Publication/Volume 51, Number 21 (Printed in USA).

# Accelerating the **Speed of Design**.

#### Avnet, your one solution for design creation.

Avnet Memec focuses on a select number of leading suppliers to provide original equipment manufacturers (OEMs) with the technical expertise you need in designing cutting edge products.

With factory trained and certified technical support, Avnet Memec specialists offer a level of technical depth that is unmatched in the industry. That translates into faster time to market for you, our valued customer. And it keeps getting better. **Avnet is ranked #1** for having knowledgeable FAEs and well-informed sales reps.\* We deliver:

- > Proactive Engineering Support

- > Factory Certified FAEs

Accelerate Time to Market.™

Visit the Avnet Design

Resource Center at:

www.em.avnet.com/drc

1 800 408 8353 www.em.avnet.com

# ED online contents

#### ONLINE ONLY

Check out these Web-exclusive articles:

#### Waveform-viewer software works with four suppliers' DSOs

www.edn.com/article/CA6373491

#### Network coprocessor serves as multimedia implant

www.edn.com/article/CA6370822

#### Gain-selectable amps compensate for bandwidth roll-off

www.edn.com/article/CA6367508

#### Two new suppliers broaden users' handheld-DSO choices

www.edn.com/article/CA6374070

#### Test tool speeds development of mobile devices and applications

www.edn.com/article/CA6374014

#### Midrange device includes SERDES function

www.edn.com/article/CA6373502

#### Spice simulator offers speed, capacity increase over competitors

www.edn.com/article/CA6373509

#### Paradoxically, RF integration may be SiGe's best friend

www.edn.com/article/CA6373171

#### **READERS' CHOICE**

A selection of recent articles receiving high traffic on www.edn.com.

#### Process coaxes carbon nanotubes into service as vias

www.edn.com/article/CA6368452

#### SDR goes to war

www.edn.com/article/CA6368441

### "Brick-wall" lowpass audio filter needs

www.edn.com/article/CA6368442

#### Fast-settling picoammeter circuit handles wide voltage range

www.edn.com/article/CA6368443

#### Voltage-regulator droop

www.edn.com/article/CA6368445

#### Abracadabra: Making system interconnect disappear with FPGAs

www.edn.com/article/CA6368447

#### Your name in lights, on your body

www.edn.com/article/CA6368455

#### Ingredients: Voice over Wi-Fi design, HDMI chips, more ...

www.edn.com/article/CA6370779

#### Rainbow LED indicates voltage with color

www.edn.com/article/CA484496

#### Circuit makes simple high-voltage

www.edn.com/article/CA419572

#### WE'RE STILL CELEBRATING

Visit www.edn.com/50th for all of the special content we prepared to commemorate our 50th anniversary last month, including:

- · An interactive time line of Milestones That Mattered

- · Four special features on overarching trends that have driven the industry and will continue to do so

- Audiocasts by Editor in Chief Maury Wright and other industry figures

- · Comments from past EDN editors

- The complete contents of EDN's prescient 25th-anniversary issue

- www.edn.com/50th

#### PRODUCT FEED

Throughout EDN's 50 years, engineers have had a taste for EDN's product briefs: concise, no-nonsense write-ups of new ICs and compo-

nents. Now, we're proud to introduce EDN Product fEEd, a centralized online location for this critical part of our coverage. We invite you to belly up to fEEd, where you'll find a daily dose of new products, as well as handy category filters that allow you to select the morsels that most interest you, be they analog or digital ICs, power components, sensors, passives, boards and systems, or software (to name just a few).

#### EDN Product fEEd:

- www.edn.com/productfeed RSS feed of the fEEd:

- www.edn.com/ProductfEEdWebBlog. xml?nid=3066

# FIRE YOUR IMAGINATION

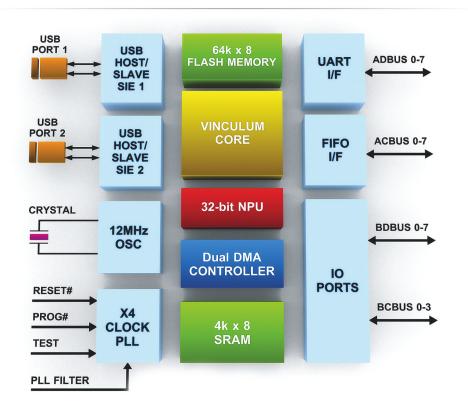

The Vinculum family of USB Host Controller not only handles the USB Host interface and data transfer functions, but owing to the inbuilt processor core and embedded Flash memory, Vinculum encapsulates the USB device classes as well. When interfacing to mass storage devices such as USB Flash drive, digital camera, or PDA, Vinculum also transparently handles the FAT File structure communicating via UART, SPI or parallel FIFO interfaces via a simple to implement command set. Vinculum provides a new cost effective solution for providing USB Host capability into products that previously did not have the hardware resources available.

#### CONNECTS

#### WITH

## Vinculum Evaluation Modules & Application Areas

The **VDIP1** module is an MCU to USB Host Controller development module for the VNC1L device and is ideal for rapid prototyping and development of VNC1L designs.

- Jumper selectable UART, SPI or FIFO MCU Interfaces

- USB "A" type socket to interface with USB peripherals

- 2nd USB Interface available via module pins if required

- Single 5V supply input

- Auxiliary 3.3V/200mA power output to power external logic

- Traffic Indicator LEDs

**VDRIVE1** is possibly the easiest solution for adding a USB Flash Drive interface to existing products. Only four signal lines plus 5V/GND are required to be connected.

- One USB "A" socket to connect to USB Flash Drive

- Link Selectable UART or SPI interface

- Only 4 signals to connect excluding PWR/GND

- Single 5V supply required

- Easy to implement command set

VMUSIC1 is a product that not only lets you add USB Flash Drive interfacing to your product but allows you to play back MP3 and other popular digital music formats direct from a USB Flash Drive.

- One USB "A" socket to connect to USB Flash Drive

- Stereo 3.5mm headphone jack socket and audio line-out connector for audio playback.

- Link Selectable UART or SPI interface

- Only 4 signals to connect excluding PWR/GND

- Single 5V supply required

- Easy to implement command set

VINCULUM - IMAGINE WHAT YOU COULD DESIGN WITH IT...

#### EDN.COMMENT

#### BY MAURY WRIGHT, EDITOR IN CHIEF

# Triple-play trickery: Beware the buzzword bandwagon

ately, it seems that almost every pitch I hear from marketers uses the term "triple play" in an attempt to leverage what they perceive as a hot market. But many of those pitchers don't even understand the meaning of "triple play," and most are stretching the truth more than a little in using it to describe their newest product. Now, I'm

not the arbiter of how to use words. But I have followed the voice-,

video-, and data-services market since before broadband data and digital video became realities. My point is to advise you to closely scrutinize anything that mentions "triple play" because I am increasingly finding that marketers are often using the hype to hide the lack of compelling features in products or to get publicity.

The term "triple play" implies a service offering from telecom carriers, MSOs (multiple systems operators), satellite operators, or maybe even power utilities. The term "triple" implies that the offering includes voice, video, and data services. The telecom carriers need the revenue from triple-play offerings to help cover the revenue shortfall they attribute to the commoditization of voice services. MSOs, at least in North America, are typically the incumbents in profitable video services and were the first to broadly offer broadband. You might think MSOs would want no part of the low-margin voice business, but, realistically, it costs almost nothing these days for them to add voice to their video and data offerings.

Triple-play offerings have attracted interest from analysts and other experts because the success of these offerings will go a long way in determining which carriers are still with us in a few years. Even the politicians

have jumped on the bandwagon, as the telecom carriers strive to offer video without signing franchise agreements with communities, as MSOs must do.

Because you read so much about triple play, vendors of ICs, boards, and even cables or power supplies are using the term to promote their products. For example, the spin doctors label home-networking products as triple-play products. Perhaps home LANs will eventually find use in distributing video around homes, but none have yet proved capable. Moreover, some, such as power-line-based HomePlug technology, will probably never carry high-definition-quality video.

There's also hype aplenty from the communication-IC crowd. Vendors of everything from Ethernet switches and network processors to traffic managers and network-search engines trumpet triple-play capability. Some of these products may prove key enablers in network equipment that service providers rely on to offer the triple play. But most of the vendors claim that their chosen technology is the only avenue to the triple play. I'd argue again that triple play is simply a service offering and consumers don't care how carriers deliver it.

Recently, companies have been

bombarding me with presentations on the theme of a converged network that carries video and voice over the same IP (Internet Protocol) transportprotocol device that delivers data. Now, I'm all for converged networks. I was editor of CommVerge magazine in the 1999 to 2002 time frame, and CommVerge focused on convergence. But we were wrong then about how quickly a converged network might become reality. And I'm still not sure how fast the carriers can broadly move to IPTV—especially when the requirement includes carrying multiple HDTV-quality streams.

Although current telecom networks aren't IPTV-capable, those networks aren't the biggest roadblock to triple-play offerings. The last mile remains the roadblock. As I recently chronicled, the carriers are just beginning to roll out IPTV-capable broadband pipes (Reference 1). The tripleplay offerings now on the market almost universally rely on an overlay network to deliver the video. And no matter how many communication-IC vendors hype their triple-play ICs, carriers will not rip up core and access networks and install new ones unless the converged network can reach the home. Even if or when the carriers move to converged networks, they will be just that: multimediacapable IP networks, not triple-play networks.

The carriers get it. They are even talking "quad-play," throwing mobile service into the bundle. And mobile services clearly don't arrive through a converged network. But the enabling-technology vendors will continue the hype.**EDN**

#### REFERENCE

■ Wright, Maury, "100-Mbps broadband: How, why, when, and where?" *EDN*, July 6, 2006, pg 48, www.edn. com/article/CA6347250.

You can reach me at 1-858-748-6785 or mgwright@edn.com.

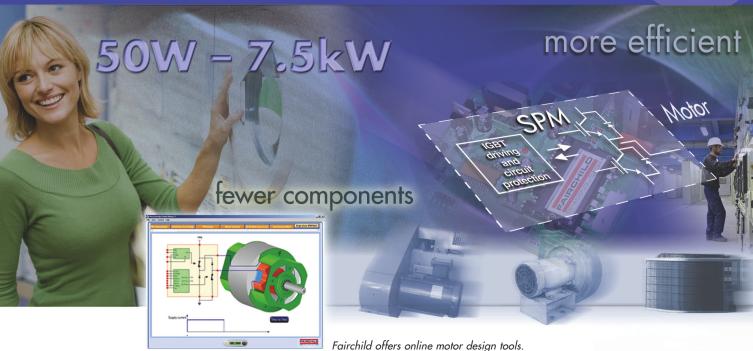

# Energy-saving inverter designs: 50% less cost, size and time.

#### Integrated power modules simplify your designs

Smart Power Modules (SPM<sup>TM</sup>) are just what you need to dramatically improve the performance/cost ratio of variable speed designs. Available for motor ratings from 50W to 7.5kW, every SPM includes:

- An integrated drive and protection solution built with our leading power components

- Fairchild's combined power and motion design expertise

- Best-in-class packaging technology that reduces board space while providing excellent thermal performance

| SPM<br>Series | Motor<br>Ratings | Description                          |

|---------------|------------------|--------------------------------------|

| Motion-SPM    | 50W to 7.5kW     | 3-phase IGBT or MOSFET inverter      |

| SRM-SPM       | 2kW              | Single-phase asymmetric bridge       |

| PFC-SPM       | 1kW to 3kW       | Partial switching converter module   |

|               | 3kW to 6kW       | Power Factor Correction (PFC) module |

Our SPM series includes solutions for consumer and industrial inverter designs, as well as options for switched reluctance and PFC.

If you prefer to build your own drive with discrete components, all the building blocks inside our SPM, including IGBTs, HVICs and MOSFETs are also available for your motion power path.

If energy and cost savings are your problem, Fairchild has your solution.

For more motor design information, including online design tools and application notes, visit www.fairchildsemi.com/motor.

problem solved

www.fairchildsemi.com

### Whatever direction you choose, Gore gets you optimal performance without speed limits.

We've got all the preferred high-speed assemblies ready-to-roll. So, fasten your seat belt!

ZD Cable Assemblies

GORETM EYE-OPENER® GORETM EYE-OPENER® AirMax VS® Cable Assemblies

GORETM EYE-OPENER® GBX Cable Assemblies

**GORETM** INFINIBAND<sup>TM</sup>/CX4 Cable Assemblies

GORE™ Microminiature Flat Cable Assemblies

GORETM EYE-OPENER® VHDM<sup>TM</sup> Cable Assemblies

W. L. Gore & Associates

**North America:** 1 (800) 445-4673 International: 1 (302) 292-5100

**Europe:** +49/91 44/6010 +44/1382-561511 gore.com

#### PUBLISHER, EDN WORLDWIDE

John Schirmer 1-408-345-4402; fax: 1-408-345-4400; ischirmer@reedbusiness.com

#### EDITOR IN CHIEF

Maury Wright, 1-858-748-6785; mgwright@edn.com

#### **EXECUTIVE EDITOR**

Ron Wilson, 1-408-345-4427; ronald.wilson@reedbusiness.com

#### MANAGING EDITOR

Kasey Clark

1-781-734-8436; fax: 1-781-290-3436, kase@reedbusiness.com

#### **EXECUTIVE EDITOR, ONLINE**

Matthew Miller

1-781-734-8446; fax: 1-781-290-3446; mdmiller@reedbusiness.com

#### SENIOR ART DIRECTOR

Mike O'Leary

1-781-734-8307; fax: 1-781-290-3307; moleary@reedbusiness.com

#### **EMBEDDED SYSTEMS**

Warren Webb, Technical Editor; 1-858-513-3713; fax: 1-858-486-3646; wwebb@edn.com

#### ANALOG

Paul Rako, Technical Editor; 1-408-745-1994; paul.rako@reedbusiness.com

#### EDA, MEMORY, PROGRAMMABLE LOGIC

Michael Santarini, Senior Editor; 1-408-345-4424;

michael.santarini@reedbusiness.com

#### MICROPROCESSORS, DSPS, TOOLS

Robert Cravotta, Technical Editor; 1-661-296-5096; fax: 1-781-734-8070, rcravotta@edn.com

#### MASS STORAGE, MULTIMEDIA, PCS AND PERIPHERALS

Brian Dipert, Senior Technical Editor; 1-916-760-0159; fax: 1-781-734-8038; bdipert@edn.com

#### POWER SOURCES, ONLINE INITIATIVES

Margery Conner, Technical Editor; 1-805-461-8242; fax: 1-805-461-9640; mconner@connerbase.com

#### DESIGN IDEAS EDITOR

Brad Thompson

edndesignideas@reedbusiness.com

#### SENIOR ASSOCIATE EDITOR

Frances T Granville, 1-781-734-8439; fax: 1-781-290-3439; f.granville@reedbusiness.com

#### ASSOCIATE EDITOR

Maura Hadro Butler, 1-908-347-9605; mbutler@reedbusiness.com

#### EDITORIAL/WEB PRODUCTION MANAGER

Diane Malone, Manager

1-781-734-8445; fax: 1-781-290-3445

Steve Mahoney, Production/Editorial Coordinator

1-781-734-8442; fax: 1-781-290-3442

Melissa Annand, Newsletter/Editorial Coordinator

Contact for contributed technical articles

1-781-734-8443; fax: 1-781-290-3443

Adam Odoardi, Prepress Manager

1-781-734-8325; fax: 1-781-290-3325

#### CONTRIBUTING TECHNICAL EDITOR

Dan Strassberg, strassbergedn@att.net Nicholas Cravotta, editor@nicholascravotta.com

#### COLUMNISTS

Howard Johnson, PhD; Bonnie Baker; Joshua Israelsohn

#### PRODUCTION

Dorothy Buchholz, Group Production Director

1-781-734-8329

Kelly Brashears, Production Manager

1-781-734-8328; fax: 1-781-734-8086

Linda Lepordo, Production Manager

1-781-734-8332; fax: 1-781-734-8086

Pam Boord, Advertising Art

1-781-734-8313; fax: 1-781-290-3313

#### EDN EUROPE

Graham Prophet, Editor, Reed Publishing

The Quadrant, Sutton, Surrey SM2 5AS

+44 118 935 1650; fax: +44 118 935 1670;

approphet@reedbusiness.com

#### EDN ASIA

Raymond Wong, Managing Director/ Publishing Director raymond.wong@rbi-asia.com Kirlimaya Varma, Editor in Chief kirli.varma@rbi-asia.com

#### EDN CHINA

William Zhang, Publisher and Editorial Director wmzhang@idg-rbi.com.cn John Mu, Executive Editor johnmu@idg-rbi.com.cn

#### EDN JAPAN

Katsuya Watanabe, Publisher k.watanabe@reedbusiness.jp Kenji Tsuda, Editorial Director and Editor in Chief tsuda@reedbusiness.jp Takatsuna Mamoto, Deputy Editor in Chief t.mamoto@reedbusiness.jp

The EDN Editorial Advisory Board serves as an industry touchstone for the editors of EDN worldwide, helping to identify key trends and voicing the concerns of the engineering community.

#### DENNIS BROPHY

Director of Business Development, Mentor Graphics

#### DANIS CARTER

Principal Engineer, Tyco Healthcare

#### CHARLES CLARK

Technical Fellow, Pratt & Whitney Rocketdyne

#### DMITRII LOUKIANOV

System Architect, Intel

#### RON MANCINI

Staff Scientist, Texas Instruments

#### GABRIEL PATULEA

Design Engineer, Cisco

#### MIHIR RAVEL

VP Technology, National Instruments

#### DAVE ROBERTSON

Product Line Director, Analog Devices

#### SCOTT SMYERS

VP Network and System Architecture Division, Sony

#### TOM SZOLYGA

Program Manager, Hewlett-Packard

#### JIM WILLIAMS

Staff Scientist, Linear Technology

EDN. 225 Wyman St, Waltham, MA 02451. www.edn.com. Phone 1-781-734-8000; fax 1-781-734-8070. Address changes or subscription inquiries: phone 1-800-446-6551; fax 1-303-470-4280; subsmail@reed-business.com. For a free subscription, go to www.getfreemag.com/edn. Reed Business Information, 8878 S Barrons Blvd, Highlands Ranch, CO 80129-2345. Include your mailing label.

# **USB**Data Acquisition

#### Low-Cost Data Acquisition Starting at \$99

- Up to 16 bits, 250 kS/s, 16 channels

- Highly portable, USB bus-powered

#### **Full-Featured, Multifunction DAQ**

- Up to 16 bits, 1.25 MS/s, 32 channels

- Isolated options for measurement accuracy and reliability

#### High-Performance, Modular I/O

- Up to 24 bits, 3.2 MS/s, 256 channels

- Modules for sensor inputs, analog I/O, digital I/O

To find the perfect USB device for your system, visit **ni.com/usb**.

(800) 327 9894

© 2006 National Instruments. All rights reserved. CompactRIO, National Instruments, NI, ni.com, and NI CompactDAQ are trademarks of National Instruments. Other product and company names listed are trademarks or trade names of their respective companies. 7778-301-101

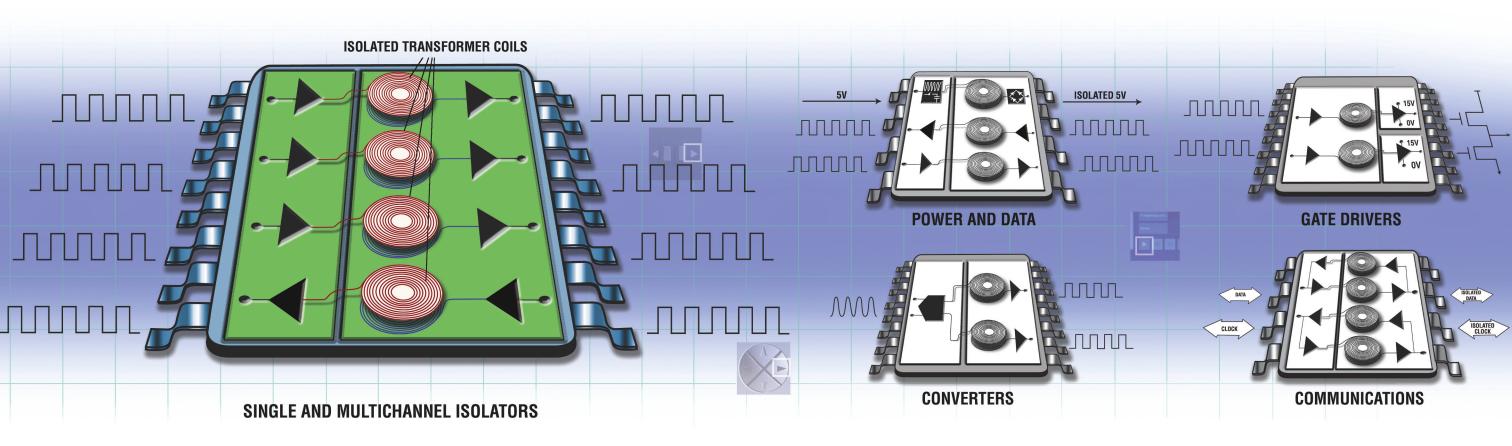

# Isolation and innovation in one package.

# With iCoupler, analog is everywhere.

iCoupler® digital isolators offer faster data rates, greater reliability, and up to 70% savings in board space and cost, vs. optocoupler solutions.

#### Single and Multichannel Isolators

Greater integration, performance, and reliability than optocouplers

#### ADuM1100/ADuM120x/ADuM130x/ ADuM140x/ADuM240x

- · Single, dual, triple, and quad

- Variety of input/output channel configurations

All pricing in \$U.S. 1k quantities unless indicated.

iCoupler products approved by UL, VDE, CSA, and TÜV.

- 2.5 kV to 5 kV isolation

- Up to 100 Mbps data rate

- Starting at \$0.55/channel

#### *iso*Power™

Industry's first digital isolator with integrated, isolated power

#### ADuM524x family

- 50 mW isolated power

- Variety of input/output channel configurations

- Dual channel, 2.5 kV data isolation

- Starting at \$2.95

#### Converters

Industry's leading converters with integrated isolation

#### AD740x family

- 16-bit, 10 MSPS

- 3.75 kV isolation ratingEnables extreme

- accuracy in current monitoring

- Starting at \$4.00

#### **Gate Drivers**

Compact isolation solution for gate drive applications

#### ADuM1230

- High side isolated from low side

- 100 mA, high-side and low-side drive

- 2.5 kV isolation rating

- Starting at \$1.85

#### Communications

Isolation tailored to specific communications

#### ADuM125x family

- True bidirectional isolation for I<sup>2</sup>C<sup>®</sup> buses

- 2.5 kV isolation ratingStarting at \$3.05

#### ADM2485

- 16 Mbps RS-485 transceiver

- Integrated transformer driver

- 2.5 kV isolation rating

- Starting at \$5.50

#### iCoupler technology: Over 75 million isolated channels

*i*Coupler technology represents the state of the art in digital isolation. Unlike common optocoupler isolation techniques, *i*Coupler combines chip scale transformer technology with analog and mixed-signal circuits for significant system level integration, cost savings, and functional advantages. These include:

- Standard isolators that offer faster data rates, greater reliability, and up to 70% savings in board space and cost

- New functionality: bidirectional data paths, combined signal and power isolation, isolation integrated with data converters, I<sup>2</sup>C, RS-485, and gate driver circuits

Eliminate the performance trade-offs of traditional isolation solutions. See why leading engineers have chosen *i*Coupler technology over optocouplers to isolate more than 75 million channels.

For complete information on *i*Coupler technology, product portfolio, white papers, application notes, samples, and more, please visit our website.

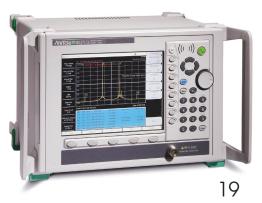

### 7.1-GHz, low-phase-noise spectrum analyzer costs \$11,995

nritsu's MS2717A spectrum analyzer offers general-purpose spectrum analysis over the 100-kHz to 7.1-GHz frequency range at a price of \$11,995. Compared with earlier instruments, increased measurement capabilities reduce the cost of and time required for analysis of RF components in wireless, aerospace/defense, and university applications. For characterizing wireless Node

At a cost of \$11,995, the MS2717A offers -110 dBc/Hz SSB phase noise and great ease of use for spectrum analysis to 7.1 GHz.

B transmitter components, the instrument offers optional WCDMA/HSDPA (wirelesscode-division-multiple-access/high-speeddata-packet-access) RF-test and detailed WCDMA-demodulation measurements.

The manufacturer boasts of the unit's low phase-noise: typically, -110 dBc/Hz SSB (single-sideband) phase noise at 10kHz offsets from carriers at frequencies to 6 GHz. According to the manufacturer, this performance allows the analyzer to easily measure most wireless local oscillators and synthesizers. Typical dynamic range of 100 dB and capture bandwidth of 8 MHz enable fast and precise testing of wireless components that require exceptional linearity. With options, the signal-analyzer-mode frequency ranges are 824 to 894 MHz, 1710 to 2170 MHz, and 2300 to 2700 MHz. An available pass/fail mode based on the five 3GPP (third-generation-project-partnership) test

#### **■ FEEDBACK LOOP**

"As always, it is prudent to check your assumptions before you commit your company's human and fiscal resources to a development path. The insight you get might surprise you."

Mark Jakusovszky in EDN's Feedback Loop at www.edn.com/article/ CA6373171. Add your comments.

models further simplifies testing.

The  $9.53\times14.65\times13.35$ -in. instrument, which weighs 12.32 lbs, includes 64 Mbytes of compact-flash memory and provides Ethernet and USB 2.0 connectivity for archiving setups, updating firmware, and transferring results.

-by Dan Strassberg

▶ Anritsu Co, www.anritsu.com.

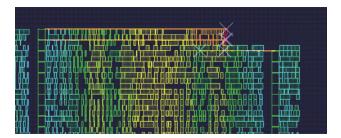

### Tool generates HDLs directly from Simulink

The folks trying to model multiple DSP functions to implement in FPGAs or ASICs using The MathWorks tools will be happy to learn that the company's latest release, Simulink HDL Coder, automatically generates cycle-accurate, bit-accurate Verilog or VHDL directly from Simulink. Before this announcement, users created Simulink-algorithm-based models of DSPs in Simulink and then had to recode them in VHDL to employ the DSP functions in FPGAs. That step will now be unnecessary, according to Ken Karnofsky, director of marketing for the signal-processingand communications-products group at The MathWorks.

Sudhir Sharma, HDL-product-marketing manager, says that users can employ the bidirectional tool to both transfer and cosimulate Verilog and VHDL into Simulink models. "You can verify testbenches, intellectual-property blocks, and legacy code in HDL in Simulink, speeding simulation," he says. Because the tool can generate HDL directly from Simulink, you can also run the HDL in FPGAs, representing a big step toward allowing software engineers to directly program designs in FPGAs. Sharma points out, however, that the tool doesn't replace a hardware engineer, because synthesis, routing, and other FPGA-programming functions are still necessary for the FPGA to work properly. Simulink HDL Coder is available for the Windows, Unix, and Linux platforms. The MathWorks offers it in a perpetual license with prices starting at \$15,000. Users must also purchase a separate Simulink license.-by Michael Santarini

>The MathWorks, www.mathworks.com.

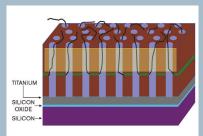

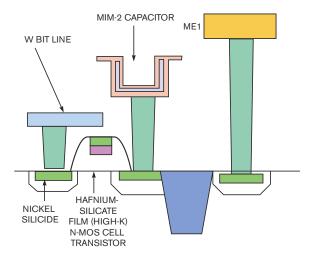

### 55-nm embedded-DRAM process debuts

any designers think of embedded DRAMthat is, DRAM arrays fabricated on logic SOCs (systems on chips)-as a technological artifact: a technique designers a few years ago tried in moderate-performance graphics chips and since superseded. But NEC Electronics is challenging that opinion with the introduction this month of a 55-nm embedded-DRAM process. An evolution of the company's previously announced, 55-nm, half-step process, this variant may succeed in bringing embedded-DRAM architectures back to center stage in a number of

SOC applications beyond just graphics controllers.

The key benefits of the process variant derive from the characteristics of its new DRAM-cell design, according to NEC Senior Design Engineering Manager Hideya Horikawa. The cell uses NEC's MIM (metal-insulator-metal)-2 capacitor structure with zirconium oxide as the high-k capacitor dielectric, the same structure the company uses for its 90-nm processes. But, in the new process, the cell measures 0.12 sq microns-a figure Horikawa believes will be at least 20% smaller than any comparable embeddedon-chip arrays as large as 4 Mbytes should be feasible.

Electrical improvements may be more important than density, however. Horikawa says that the new cell enables 200-MHz cycle rates on full arrays. This feature combines with low operating power to open many new possibilities. The speed and the ability to have wide connections to the array and the flexibility to creatively organize the DRAM macros-in rich multibank schemes, for example-mean that in-system performance of even a large on-chip memory can far exceed what would be possible with external DRAM.

This feature, in turn, suggests that the approach may indeed be useful for applications outside stereotypical embedded-graphics frame buffers. NEC Custom SOC Solutions' vice president and general manager, Kazu Yamada, says that a number of design teams in both the United States and Japan are looking at this generation of embedded DRAM as an addition to the memory hierarchy in nongraphics applications. For example, considerably denser than and with a thousandth the soft-error rate of SRAM but with a speed between that

DRAM cell. So, in practice,

### **FROM THE VAULT**

Will an elite arise if one group of people gains the ability to access information before others, either because they are the developers of the information systems or because they can more easily afford those systems? Will the rich nations get richer and the poor poorer merely because the former possess the resources to develop sophisticated information systems? ... Will society tolerate the condition?

EDN, Oct 14, 1956, pg 39

of small SRAM arrays and external DRAM, the structures can act as L2 or L3 caches or as explicitly managed working storage in on-chip multiprocessing systems. This feature can eliminate the headaches of balancing the proliferation of large on-chip SRAM arrays against the complexities of extracting anything approaching theoretical bandwidth from a shared external DRAM.

There is a price to pay: The embedded-DRAM variant adds nine mask steps to the standard 55-nm CMOS process. But-significantly-it does not alter the CMOS-logic structures. So, all intellectual property for the vanilla, 55-nm logic process works with the embedded-DRAM variant, as well. NEC expects to deliver embedded-DRAM macros to design teams by the end of 2006 and to begin production on the 55-nm process in the second half of 2007.

-by Ron Wilson ▶NEC Electronics, www. necel.com.

NEC's 55-nm MIM-2 embedded-DRAM cell combines a 0.12-sqmicron area with a 200-MHz system speed.

#### **DILBERT By Scott Adams**

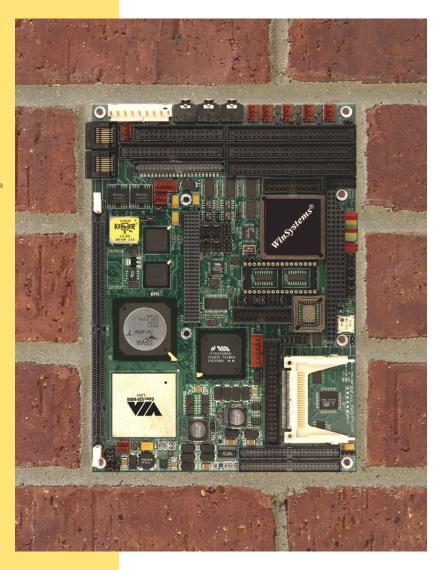

# BUILT TO LAST

# Fanless EBX 733MHz P3 with COM, dual ENET, USB and Video

- VIA 733MHz or 1GHz C3 CPU

- PC-compatible, supports Windows<sup>®</sup>

XP, CE, Linux and x86 RTOS

- Up to 512MB PC133 SDRAM

- Up 1GB bootable DOC®, 512KB SRAM, or 1MB EPROM

- Type I and II CompactFlash cards supported up to 2GB

- CRT, flat panel, and LVDS

- Two 10/100 Ethernet controllers

- Four USB ports

- Four serial COM ports

- LPT, Kybd, and mouse

- 48 bi-directional I/O lines

- Two EIDE and one floppy disk controller

- AC97 Audio supported

- PC/104 & PC/104-Plus expansion

- +5 volt only operation

- EBX size: 5.75" x 8.0" (146 mm x 203 mm)

- -40° to +85°C operation (733MHz)

- Quick Start Developers Kits for Windows® XP, CE, and Linux

- Immediate availability

The EBC-C3 embeds 9 different functions to provide a processor- and I/O-intensive solution. It operates over a -40° to +85°C temperature range without the need of a fan, making it ideal for embedded applications such as robotics, MIL/COTS, transportation, pipeline, and machine control.

It runs Windows® CE, Windows® XP embedded, Linux, and other operating systems as VxWorks and QNX. And its x86-PC software compatibility assures a wide range of tools to aid in your application's program development and checkout.

Call 817-274-7553 or Visit www.winsystems.com

Ask about our 30-day product evaluation!

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

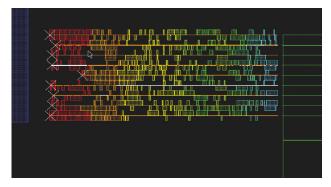

### Test products support PCI Express, HDMI

Technologies gilent has announced what it calls the industry's first complete and integrated ×1 through ×16 protocol analyzer and exerciser system for 5-Gbps PCle (PCI Express) 2.0, which doubles the 1.x protocol's speed. The E2960B series addresses the industry's need for a single protocol-test suite that provides nonintrusive measurement of PCIe signals, LTSSM (link-training-and-status-statemachine) testing, and crosssystem measurements.

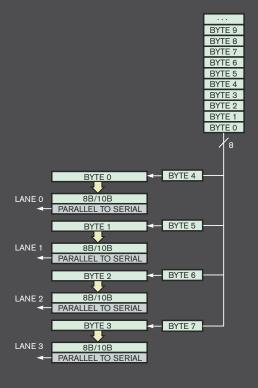

Increasing PCle's speed to 5 Gbps presents significant challenges to designers of computer and communication systems. The series comprises an analyzer and an exerciser that support both PCIe 1.x and 2.0. Multiple probing options, as well as the newly invented P2L (protocol-to-logic) gateway, complete the system. The analyzer features probes in the midbus 2.0 series that improve upon the current soft-touch midbus probes. The new probes' capacitive loading is less than 0.15 pF; sensitivity is as low as 60 mV.

Before the introduction of the E2960B series, logic and protocol analyzers were separate products. The new series combines key features of both into a single product that enables users to understand data from the physical layer to the transaction layer. Capabilities include the per-lane view, which shows 8-bit/10-bit data even before channel bonding has completed, and the trigger-down-the-lane view, which enables triggering on

Before the introduction of the E2960B series, logic and protocol analyzers were separate products. The new series combines key features of both into a single product that enables users to understand data from the physical layer to the transaction layer.

ordered sets. Per-lane LEDs provide immediate feedback on lane status.

In addition, the P2L gateway connects the logic and protocol analyzers, allowing cross-triggering and marker correlation. Connecting multiple instruments and driving them from one station enables broad visibility into the different parts of a system, such as the frontside bus and PCIe, without requiring customers who need only a protocol analyzer to purchase an entire logic analyzer. Prices start at \$47,600.

The company also recently announced an updated version of its PCIe electricalperformance-validation and -compliance software, which enables design engineers to test devices to ensure compliance with the PCle 1.x and 2.0 electrical specifications for add-in cards and motherboard systems. The N5393A software, which runs on Agilent 54855A Infiniium oscilloscopes and 80000-Series oscilloscopes, allows users to automatically execute PCle electrical-check-list tests and display the results in a flexible HTML-report format. Besides the measurement data, the report provides a margin analysis that shows how closely the tested device passed or failed each test. The list price is \$3000.

Agilent also announced an integrated sink, source, and cable-test system for the new HDMI (High-Definition Multimedia Interface) 1.3 standard. The system performs manual and automated HDMI-physical-layercompliance tests, as well as margin testing and characterization in R&D and manufacturing. Target customers include manufacturers of consumer-electronics products, semiconductor devices, and cables.

Key elements of the new system include Infiniium oscilloscopes; a TDR (time-domain reflectometer); a parallel-BERT (bit-error-ratio tester)based TMDS (transition-minimized-differential-signaling) signal generator; extensions to the N5590A test-automation software; and HDMI-specific accessories, including the new N1080A-series TPA (test-point-access)-assembly adapters. Point-and-click operations control the integrated system. Compared with previous approaches, the fast calibration time and test throughput increase productivity as much as 50%. Prices start at \$165,000, depending on the configuration.

-by Dan Strassberg **►Agilent Technologies**, www.agilent.com/find/pcie2, www.agilent.com/find/HDMI.

#### - FEEDBACK LOOP

"This article not only provides a method by which magnetic coupling can be measured, but also provokes interest in the interference medium, which was for the most part ignored or misunderstood until the associated problems became apparent to the design engineer. Now, he has the opportunity for avoidance and a way to tell how well he has done."

Bill Singleton in EDN's Feedback Loop, about a recent article on magnetic-field measurements. Read the full article and add your comments at www.edn.com/article/CA6351292.

Design Reuse

Board Integration HW/SW Partitioning

# Think Embedded? Peripherals

**Need to Customize** Verification

Custom Instructions Multi-Core Design

Get There First

When it's time to design your next embedded system, think Altera. Use our FPGAs for coprocessing or peripheral expansion for your CPU. Or use our Nios<sup>®</sup> II soft-core processor to quickly create your own stand-alone custom microcontroller. Either way, Altera offers the flexibility to improve your team's productivity and time-to-market while lowering system cost and reducing the risk of obsolescence.

If you're thinking of your next embedded design, think FPGAs—think Altera.

- World's top 20 electronic OEMs are already using Altera embedded solutions

- Over 15,000 Nios II licenses worldwide

- Support for industry-standard tools and operating systems

The Programmable Solutions Company®

www.altera.com

### "Lite" version of IP interconnects hardware blocks

hile it has been busy licensing its wares into some of the most influential platform designs in the industry, including Texas Instruments' (www. ti.com) OMAP (Open Multimedia Applications Platform) architecture, Sonics has been in an uphill battle to define the concept of interconnect IP (intellectual property). To some engineering minds, interconnect is a physical structure that results from layout and routing. To others, interconnect is a set of architectural decisions. Neither definition fits a traditional notion of IP. To further complicate things, Sonics provides not a core but a development environment, permitting architects to model a blocklevel-interconnect scheme at a rather abstract level and then nearly automatically move from the high-level model to an RTL (register-transfer-level) implementation. To some engineers, this product seems a lot more like an EDA tool than like an IP core.

The current product, the Sonics MX (multiservice-exchange) interconnect IP, includes a high-level modeling environment. It also includes a set of interface stubs that allows use of either Sonics' own OCP-IP (Open Core Protocol International Partnership) block wrappers or blocks with AMBA (Advanced Microcontroller-Bus Architecture) AXI (Advanced Extensible Interface)- or AMBA AHB (Advanced High-Performance Bus)-compliant interfaces. Additionally, the product features a tool kit of switched and shared-bus fabrics, buffers, and control blocks. The tool set weaves Chip designers may find that just hooking the blocks together is only the beginning of the problem.

these hardware components into an interconnect structure that ties the user's hardware blocks in a way that meets the performance, power, and quality-of-service requirements that developers design during architectural simulation.

This approach has worked well for the most challenging SOC (system-on-chip) designs, in which both the number of blocks and the interblock-traffic requirements make the design highly complex. But the appeal has been less obvious to less complex designsthose CPU-centric chips with few processors that hover on the boundary between traditional ASICs and SOCs. As these designs get more complex, they start to benefit from the Sonics approach but still can't afford the overheadeither in silicon or dollars-that makes sense on an extremely complex, high-margin chip.

To address what they feel is an emerging market in these less complex chip designs, the Sonics folks have come up with LX (lite exchange), a scaled-back version of MX. Many of the underlying hardware elements are the same, but the LX package offers what Sonics somewhat vaguely calls "a reduced set of design features." The aim is to produce interconnect structures for mid-

sized SOCs that are appropriate in both space and power for the smaller problems the tools address but still convenient enough to the design team to justify the expenditure.

This approach may be a hard sell for some teams moving up from simple single-processor ASICs to moderately more complex designs. Such teams have typically developed some facility with AMBA or some other proprietary interconnect architecture and won't see the added value of an interconnect-generating tool. Yet, as these chip designers confront some

of the system-level challenges of SOCs, such as optimizing access to a shared DRAM pool, quaranteeing quality of service, providing system-level exception handling, and offering hardware-level security that can meet digital-rights-management requirements, they may find that just hooking the blocks together is only the beginning of the problem. In these cases, an architecture-level interconnect tool capable of RTL generation is indeed worth a look.-by Ron Wilson

Sonics Inc, www.sonicsinc.

# DOWNCONVERTER SIMPLIFIES WIDEBAND APPLICATIONS

Tackling high-performance applications, such as wideband recording, real-time digital-signal processing, software radio, telemetry, and radar-beam forming, Pentek recently released the high-speed, dual-channel Model 6821-422 ADC in a 6U VME form factor. The 6821-422 digitizes the incoming signal at 215 MHz and delivers identical sample streams to two independent digital-downconverter FPGA cores. Within each core, an input stage allows scaling of the ADC samples by a 16-bit gain term.

A direct-digital-frequency synthesizer core generates the desired center frequency and delivers two com-

plex local-oscillator signals, offset slightly in phase, to two complex digital mixers that perform frequency translation of the input signal to 0 Hz. The digital output signals are available on two or four front-panel data-port connectors using several data-packing modes. Pentek's C-callable ReadyFlow board-support libraries are available. Prices for the Model 6821-422 module start at \$17,495.—by Warren Webb

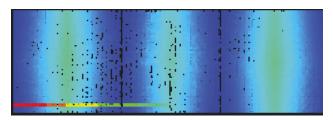

The Model 6821-422 preconfigured digital-software-radio subsystem accepts an analog-RF input and delivers real or complex digital-output samples translated to baseband from any frequency slice of the input signal.

BioLock™, from Weiser Lock®, a Black & Decker® company, and technology from Corporation

Rights Management

Open Source

Car Telematics

IPTV

Mobile TV

Driver Assistance

#### Biometrics

Streaming Media

High Definition

Effects Processing

Triple Play

Audio Processing VolP

Embedded Security

GSM/EDGE

Baseband Processing

Digital Radio

Global Positioning

GCC/Linux

#### **Bringing biometric security home**

What's the key to making biometric security affordable for consumers? The Blackfin® Processor. Developed by Sequiam in conjunction with Black & Decker,® BioLock™ can store up to 50 users' fingerprints—then Blackfin matches them with new input in less than one second And Blackfin makes BioLock a complete standalone system; there's no external server or power supply. In fact, BioLock runs for one year on just 4 AA batteries. So Blackfin is everywhere, keeping you safe and sound.

Get started using Blackfin now: analog.com/blackfin-is-everywhere

#### M RESEARCH UPDATE

BY RON WILSON

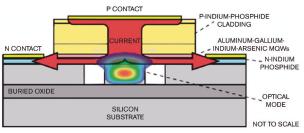

Bonding an indium-phosphide layer over a conventional silicon waveguide, Intel and the University of California-Santa Barbara researchers have demonstrated an electrically pumped laser that requires no precision assembly.

#### LASER ON A CHIP TARGETS TERABIT RATES

orking with a team at the University of California-Santa Barbara, Intel developers have demonstrated a technique for fabricating very small lasers on the surface of otherwise-conventional silicon ICs without demanding precision alignment or assembly steps. The process could lead to routine use of on-chip lasers for interconnect purposes and, Intel claims, to terabit data rates between chips.

The process starts with the fabrication of a silicon waveguide in an SOI (silicon-oninsulator) wafer. The waveguide has reflective ends to act as a tuned cavity. The researchers bonded a layer of indium phosphide over the entire wafer using low-temperature oxide-bonding techniques. The ability to achieve a strong bond at 300°C is critical, the researchers say, because it makes the step compatible with standard silicon back-end-of-line processing. Finally, the team implants, etches, and contacts the indium-phosphide layer to form an electrically pumped light source directly over the silicon wavequide.

In operation, electrical cur-

rent higher than approximately 60 mA stimulates photon emission from the indiumphosphide layer. These photons stimulate the tail of a waveguide optical mode that extends up into the interface. This added energy, in turn, stimulates the photon-emission behavior of the silicon, triggering lasing. Researchers have fabricated these devices that operate at 1577 nm at temperatures slightly in excess of 20°C.

- **▶Intel Corp**, www.intel.com.

- **DUniversity of California**-Santa Barbara, www.ucsb. edu

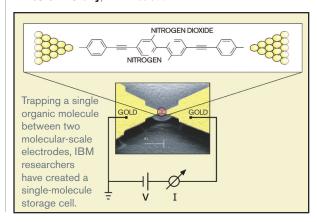

### 1.5-nm organic cell encapsulates memory

esearchers at IBM's Zurich Research Laboratory have demonstrated a stable, reprogrammable, nondestructive-read-memory effect in a single organic molecule less than 2 nm long. Technicians at Rice University (Houston) custom-designed and synthesized the molecule, BPDN-DT (Bipyridyl-Dinitro Oligophenylene-Ethynylene Dithiol). The Zurich team then devised, in effect, a micromechanical vice to hold the molecule and establish electrical contact with its ends. The team accomplished this goal by fabricating an extremely thin metallic bridge on a flexible insulator and then flexing the insulator until the bridge just tears apart. Researchers then introduce a solution containing the organic molecules and begin to relax the stress. As the two broken fragments of the bridge close together, the desired molecule orients itself between them and becomes fixed.

The Zurich team showed that the molecule exhibited two distinct conductive states and that the team could repeatedly switch between them by applying voltage pulse. The researchers demonstrated endurance of 500 cycles and microsecond-level switching times.

- ▶IBM Zurich Research Laboratory, www.zurich.ibm.com.

- ▶ Rice University, www.rice.edu.

#### Mechanism interlocks nano-oscillators

Scientists can force the oscillation at microwave frequencies of nanoscale sandwiches in which a layer of copper film separates two layers of magnetic film. However, the resulting devices produce output power on the order of 10 nW-not particularly useful in most applications. They recently discovered, however, that if they placed such nanooscillators in an array, the devices would phase-lock to each other, and the resulting power output would increase as the square of the number of active devices. However, they did not understand the mechanism for this synchronization.

Researchers at NIST, Seagate Research Center, and Hitachi Global Storage Technologies now know why: The oscillators communicate by means of wave patterns that occur in the spins of the electrons in the material between them. The finding is important for its implications in the world of "spintronics," in which researchers encode information into electron-spin patterns instead of into electron-motion patterns.

- National Institute of Standards and Technology, www.nist.gov.

- Seagate Research Center, www.seagate.com.

- Hitachi Global Storage Technologies, www.hgst.com.

#### Audio Processing

Triple Play VoIP

Embedded Security

GSM/EDGE

Baseband Processing

Digital Radio

Global Positioning

Packet Processing

GCC/Linux

Cryptography

Rights Management

Open Source

Car Telematics

#### One processor plays many parts

Musicians trust Roland for the best home studio recording equipment. So when Roland realized a separate DSP and microcontroller stood in the way of a superior audio interface, it auditioned the Blackfin® Processor. Blackfin's architecture enabled the TOPPERS/JSP RTOS to port easily—and perform better at running the entire user interface. While its DSP performance, operating at just 400 MHz, easily delivered 10 channels in/out and up to 24-bit/192 kHz audio capture. Now Blackfin is everywhere, making musicians' dreams come true.

Get started using Blackfin now: analog.com/blackfin-is-everywhere

#### GLOBAL DESIGNER

### Develop software early on virtual ARM hardware

esigners of complex microprocessor-based systems often face the problem of having to develop software before their hardware is ready. According to officials at ARM, that problem becomes particularly acute for developers of highspecification consumer multimedia products. But conventional software-based simulations often run too slowly to be useful. To address the problem, the company has created Realview System Generator, a tool that allows ARM-platform developers tobuild instruction-accurate models that software engineers can use to verify software behavior, because the models run nearly at operating speeds.

The tool operates in a graphical, drag-and-drop style: Users choose blocks from a standard library that includes not only basic ARM-processor elements, but also the company's TrustZone hardware-security and Jazelle Java-acceleration technologies. ARM integrated these tools into the Realview tool flow. Users can debug their models and then use the Realview real-time-system-model graphics-modeling package, which mimics the proposed final form of the product, to test the full user experience with software running. However, the stand-alone-software models do not run within the tool set. They support an operating system with applications running above and still operate at speeds close to those of processors in typical portable products. The model removes as much low-level detail of the hardware implementation as possible and maintains instruction accuracy, ARM says. The company owns the IP (intellectual property) to certify the models as fully accurate.

The speed comes from a translation technologysomewhat similar to a software interpreter-that dynamically translates ARM instructions, block by block, into native instructions for the host processor (Windows and Linux environments on an X86 architecture), holding each block in cache. Peripherals become active only when the system calls them, so the model does not use resources, constantly monitoring their status.

ARM intends that software developers, of whom only a small percentage now use simulation, and professionals creating content in graphics and multimedia-authoring packages use the models. ARM says it will encourage third-party developers within its own product ecosystem to provide models to expand the system; the tool currently supports ARM926EJ-S, ARM1136JF-S, and ARM-1176JZF-S cores.

> -by Graham Prophet, **EDN** Europe

**ARM**, www.arm.com.

#### 3G subscriptions to reach 285 million worldwide by year-end

After years of market uncertainty, with investors wringing their hands and restructuring their finances, 3G has finally gained credibility, according to ABI Research. Jake Saunders, the company's Asia-Pacific director, says, "3G subscriptions, including CDMA [code-division multiple access] 2000, are forecast to hit 285 million by the end of 2006. Operators' overall capital expenditure will grow for the fourth year to reach \$126.4 billion, and annual 3G-related handset shipments should pull past 300 million."

W-CDMA (wideband CDMA) is starting to pull its weight in the 3G stakes and is expected to overtake CDMA 2000 by about 2012, but CDMA 2000 is not down for the count: It has proved to be an efficient approach. Nevertheless, W-CDMA will continue to keep the pressure on, and, as end users replace their GSM (Global System for Mobile communications) handsets, many will default to purchasing a W-CDMA handset, providing manufacturers with increasing economies of scale.

But not even W-CDMA backers can afford to stand still. TD-SCDMA (time-division-synchronous CDMA) may be taking time to reach commercial reality in China, but Chinese infrastructure vendors, such as Datang Mobile (www. datangmobile.cn/en), are re-engineering their technolo-

gies to offer a hybrid TD-SCDMA/HSDPA (high-speeddownlink-packet-access) technology that makes the most of both methods. Don't underestimate WiMax, either. These access technologies dictate the overall cost of service delivery and the functions of the valueadded services that operators offer. They also determine which camps of vendors-and their upstream- and downstream-component suppliers-will receive the lion's share of the equipment-spending pie. Intangible factors, such as legacy equipment integration, access to towers, back-haul infrastructure, handset lineups, and vendor financing, also enter the equation.

"The exciting prospect is that national markets could be opening up to alternative access technologies more than ever before," says Saunders. "If the vendors of the new alternative 3G+ solutions can demonstrate that they can operate alongside existing 3G and even 2G infrastructures, the opportunities for new entrants or even a few industry veterans, such as Qualcomm (www.qualcomm.com) and Lucent (www. lucent.com) could suddenly look a lot brighter."

−by Vinod Kataria, *EDN Asia*

ABI Research, www.abiresearch.com/home.jsp.

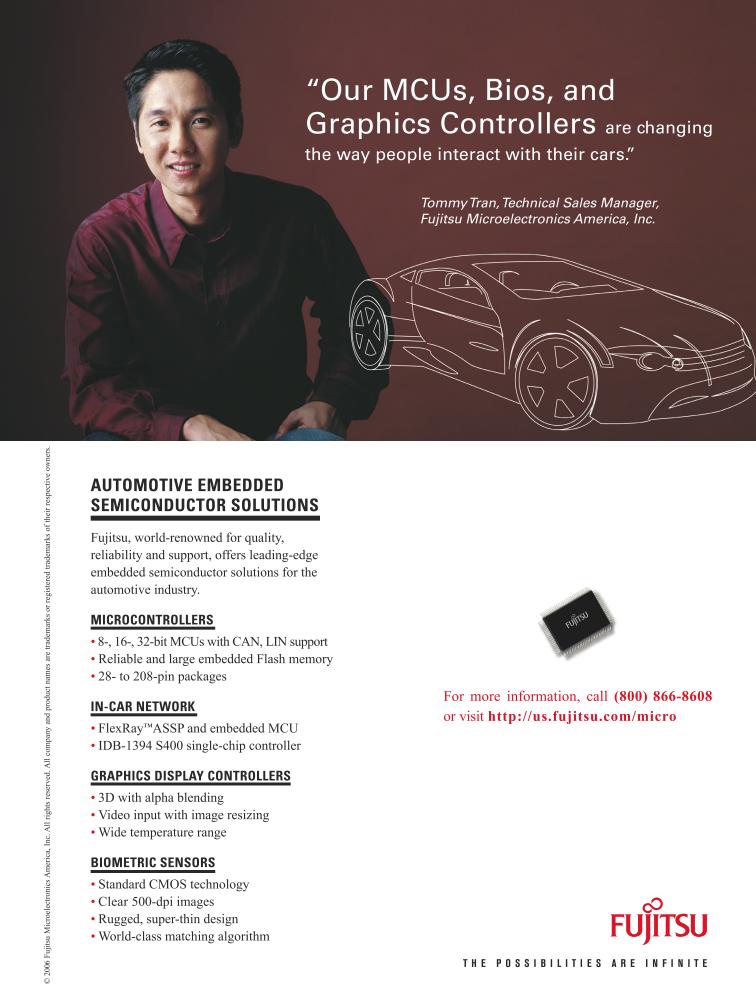

#### **AUTOMOTIVE EMBEDDED SEMICONDUCTOR SOLUTIONS**

Fujitsu, world-renowned for quality, reliability and support, offers leading-edge embedded semiconductor solutions for the automotive industry.

#### **MICROCONTROLLERS**

- 8-, 16-, 32-bit MCUs with CAN, LIN support

- Reliable and large embedded Flash memory

- 28- to 208-pin packages

#### **IN-CAR NETWORK**

- FlexRay™ASSP and embedded MCU

- IDB-1394 S400 single-chip controller

#### **GRAPHICS DISPLAY CONTROLLERS**

- 3D with alpha blending

- Video input with image resizing

- Wide temperature range

#### **BIOMETRIC SENSORS**

- Standard CMOS technology

- · Clear 500-dpi images

- Rugged, super-thin design

- World-class matching algorithm

For more information, call **(800) 866-8608** or visit http://us.fujitsu.com/micro

V I R T U O S O

Announcing the new Cadence Virtuoso custom design platform: only the most innovative new solution can inspire the most innovative new thinking. www.cadence.com/newvirtuoso

///2/(START)/// 63/-<</0081677/::// ///**12653**//>**8**//\*\*--{{}}:) 88/483//[8840]//::(000121)/--065=0U812:/-\*--38}////093200 8/{88498}/-\*\*//9938500{099}87 3358330/55{8839500//\*//5839002 088903-3868\*\*0//59030{59840}998 8350//5929\*548\*\*W8399/238493//30 [7950983/\*::5638(5530)5849]58300//54 94523/6\*904(34)5[745]/654\*680{654}9 26/54\*37(\*63478)349[45]40/3830//:309 (779:<348){\*\*/})84030/84890//R42{RUN} minum [PRECISION + PREDICTABILITY]SPEED = The new Virtuoso® custom design platform from Cadence® provides an exceptionally fast and siliconaccurate way to design custom analog, RF and mixed-\* Integrated products on a common database address complex design requirements across process nodes. >>> \* Automated constraint management connects the electrical and physical design domains for the first time—helping maintain design intent within the flow, and across globally distributed design chains and customers. >>>>>>>>> \* High-speed, comprehensive simulation engines enable constraint refinement, and a brand new custom floorplanner allows analog design teams to rapidly explore multiple design \* New layout techniques and integrated DFM yield the best, most differentiated custom silicon possible. >>>>>>>> \* This next-generation platform enables designers to focus on the task of precision crafting, leaving the mundane to automation. <<<<< www.cadence.com/newvirtuoso >>>>>> ([(934)8--\*30890/\*-\*002/1030/8(8)7////#</0%8677:/ (90)8031///125630[59]653/->8/\*\*{{8764898}}0\*9) 3432011(57\*89)82{//78//483//[8840]//::(000121 <699{5}158(57)300[4-\*}0012:/{77638}093>> **{889/:504(35/8)0764938}//\*-/99385//\*089** 9//640/8/8(99)90{84}50/577{543090}30 <87:78/5-9\*600(3)1\*/6\*940-:\*68500 /64//750/6850(59)/54194{0375096} 48/\*458(975\*45^0)00/59-03/5// 569(345/7[35]91)7/935\*30 (53/\*487[79]37345) 93U39/57/30:/3 @0{END}

cādence<sup>™</sup>

### Monolithic op amps: A lab tool became indispensable

n the early days, op amps were laboratory curiosities. Based on combinations of discrete tubes and later transistors, op amps formed the basis of analog computers that engineers used to model functions, such as addition or even integration. Some early models even came in wooden boxes. But with the advent of the monolithic op amp in 1963, the device became a hit as a component in system designs.

Robert Widlar of Fairchild (www. fairchildsemi.com) developed the first op amps, the µA702 in 1963 and the µA709 in 1965, before moving on to develop the LM101 at National Semiconductor (www.national.com). In 1968,

he wrote a forward-looking-trend article on future op-amp developments as part of EDN's first op-amp directory. You'll find an excerpt of that story below and the complete original article on our Web site at www.edn.com/article/CA6371161.

Over the 38 years since Widlar penned his article, engineers have found every imaginable use for op amps, both as discrete ICs and increasingly as elements in larger IC designs. Within EDN's special 50th-anniversary issue, Analog Devices luminary Lew Counts chronicles the amazing performance gains in op amps over the years and the process-technology advancements that made such improvement possible (see "How miniaturization beats the heat," EDN, Sept 28, 2006, pg 174, www.edn.com/060928mini). Counts argues that such analog innovation is equal to Moore's Law in terms of enabling miniaturization.EDN

#### **FUTURE TRENDS IN IC OPERATIONAL AMPLIFIERS**

Over the last five years, some outstanding advances have been made in monolithic operational amplifiers. These devices have progressed from the point where they were an expensive curiosity, with marginal performance and doubtful availability, to where their performance is definitely competitive with discrete component amplifiers.

At the same time, prices have dropped, in many cases to a level where it is impossible for discrete-component amplifiers to compete with monolithics in general-purpose applications. Further, multiple-sourcing has become a reality that, in addition to its purchasing advantages, demonstrates that the manufacture of these circuits is not entirely a black art.

The future for monolithic amplifiers indeed looks bright. However, there are many areas in which substantial improvement over present-day devices is needed. Foremost among these are the requirements for lower input currents and higher speed operation. But to gain some insight into the problems of general-purpose op amps, it is advisable to look at all of the parameters that describe their operation, pointing out where improvement is needed and then discussing how it might be done.

Monolithic amplifiers, which inherently have excellent component matching, already provide offset voltages and thermal drifts that are considerably better than discrete amplifiers. In addition, the close thermal coupling among components minimizes the effect of thermal gradients and gives fast recovery from gross overload conditions. Nonetheless, obtaining offsets lower than about 3 mV is a matter of selection, with attendant yield reductions, so great improvements in offset voltage specifications cannot be expected.

It is possible, however, to use adjustable thick-film

resistors with the monolithic amplifier to balance out the offset. Techniques are available that use a laser beam to trim the resistors after the complete circuit has been assembled. If this were done, it would be possible to guarantee better drift specifications because the voltage drift could be 100% tested on a go/no-go basis.

Undoubtedly, the strongest factor determining future op-amp designs will be the type of input stage that can give the lowest input current with about the same offset voltage as is currently obtained. At present, integrated op amps using bipolar transistors give input currents of about 100 nA. Many military-temperature-range applications require input currents less than 1 nA, and there are a large number of industrial and instrumentation applications calling for input currents less than 100 pA. Among components now known, the candidates for the input stage are improved bipolar transistors, junction FETs, and MOS FETs.

Perhaps the most straightforward way to get low input currents is to use junction field-effect transistors in the input stage. With discrete devices, input currents in the picoampere range can be realized over a 0 to 70°C temperature range. One disadvantage of FETs is that they do not tend to match well.

Even so, one can expect to see monolithic amplifiers with FET inputs within the next six months. These will give considerably improved input current specifications over the industrial temperature range, but at the expense of offset voltage and offset voltage drift. The success of these devices will depend heavily on elimination of production difficulties and on achievement of reasonable yields since industrial-range devices sell solely on cost.

-by RJ Widlar, EDN, June 10, 1968

# ANALOG edge<sup>sm</sup>

Expert tips, tricks, and techniques for analog designs

Vol. IV, Issue 10

# Amplifier Closed-Loop Bandwidth Considerations in High Resolution A/D Converter Applications

By Jerry Freeman, Applications Engineer

#### **Amplifier Bandwidth Limitations**

mplifier closed-loop bandwidth-limited accuracy considerations are critical when driving high resolution A/D Converters (ADCs). It is useful to be able to predict, for any closed loop gain, the required gain-bandwidth (GBW) product of an op amp to achieve a specified level of accuracy in terms of the minimum ADC resolution. Other sources of error include offset, noise, and distortion, which are beyond the scope of this article. A simple equation will be developed below that relates the minimum closed-loop bandwidth of an op amp to the resolution requirements of a given ADC.

Assuming a single pole roll-off, the frequency dependence of an amplifier's closed-loop gain,  $A_{CL}$ , is given by:

$$Aci = \frac{A_{CLDC}}{\sqrt{1 + \left(\frac{f}{f_{-3 dB}}\right)^2}}$$

Equation 1

where  $A_{CLDC}$  is the amplifier's DC gain, and  $f_{-3\ dB}$  is its corner frequency.

This equation describes the op amp's closed-loop gain at frequency f, in terms of the amplifier's corner frequency.

The vast majority of op amps employ internal lag compensation with a single dominant pole that rolls off the open-loop gain, from its cut-off frequency, to unity gain (zero dB) at a 20 dB per decade rate. The frequency response of such an amplifier with feedback is therefore also the same as for an RC low-pass filter. The frequency where the open-loop gain crosses unity gain is routinely called the GBW product in op amp datasheets. The GBW product for an amplifier is the product of its open loop gain (constant for a given amplifier)

-3 dB cut-off frequency, f<sub>U</sub>

Figure 1. Normalized bandwidth curve for an op amp in unity gain (Curve assumes an open loop gain with a single pole roll-off.)

and its -3 dB bandwidth (GBW product = gain x -3 dB bandwidth). Given the GBW product and the open-loop gain roll-off of -20 dB per decade, the -3 dB bandwidth for any closed loop gain can be easily calculated, from

$$BW = GBW / A_{CI}$$

Equation 2

For example, the LMP2011 with a GBW product of 3 MHz will have a bandwidth of 300 kHz when configured with an  $A_{\rm CL}$  of 10 V/V. However, at -3 dB the closed-loop gain has a 29.3% gain error. In reality, the gain expression starts rolling off long before the -3 dB pole frequency is reached. It is important to determine the frequency at which the closed-loop gain error increases above the maximum error allowed for a given data error. The maximum error in data

**Dithered Switching Frequency**

#### **Featured Products**

# Single/Dual, High Precision, Rail-to-Rail Output Operational Amplifier

The LMP2011/12/14 (single/dual/quad) are part of the LMP<sup>™</sup> family of precision amplifiers that offer an industry leading gain bandwidth of 3 MHz, while maintaining high precision and low drift over time. These amplifiers deliver excellent CMRR (130 dB) and PSRR (120 dB) ratings without frequency related noise (no 1/f). The high CMRR allows for high accuracy across voltages.

The LMP2011/12/14 deliver a very low input offset voltage which offers high accuracy measurements with continued accuracy over temperature. The low voltage noise increases signal accuracy during low frequency measurements. No external capacitors are required.

#### **Features**

- Low guaranteed V<sub>OS</sub> over temperature 60 μV

- Low noise with no 1/f, 35 nV/√ Hz

- High CMRR 130 dB

- High PSRR 120 dB

- High A<sub>VOI</sub> 130 dB

- Wide gain-bandwidth product 3 MHz

- High slew rate 4 V/µs

- Low supply current 930 μA

- Rail-to-rail output 30 mV from rails

The extended temperature range of -40°C to 125°C allows for operation in demanding industrial and automotive applications, as well as in precision instrumentation amplifiers, thermocouple amplifiers, and strain gauge bridge amplifiers. The LMP2011 is offered in SOIC-8 and SOT23-5 packaging. The LMP2012 is offered in SOIC-8 and mini SOIC-8 packaging. The LMP2014 is offered in TSSOP-14 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/LM/LMP2011.html www.national.com/pf/LM/LMP2012.html www.national.com/pf/LM/LMP2014MT.html

# Low Power, 200 kSPS to 500 kSPS, 8/10/12-Bit A/D Converters

The ADC081S051, ADC101S051, and ADC121S051 are low-power, single channel, CMOS 8/10/12-bit Analog-to-Digital Converters (ADCs) with a high-speed serial interface. Unlike the conventional practice of specifying performance at a single sample rate only, these ADCs are fully specified over a sample rate range of 200 kSPS to 500 kSPS.

Operation with a single supply can range from +2.7V to +5.25V. Normal power consumption for the ADC121S051 using a +3.6V or +5.25V supply is 1.7 mW and 8.7 mW, respectively. The power-down feature reduces the power consumption to as low as 2.6  $\mu$ W using a +5.25V supply.

#### **Features**

- Speed range: 200 kSPS to 500 kSPS

- Integral Non-Linearity (INL):

- +0.45, -0.40 LSB (ADC121S051)

- +0.15, -0.09 LSB (ADC101S051)

- +0.06, -0.05 LSB (ADC081S051)

- Differential Non-Linearity (DNL):

- +0.5, -0.25 LSB (ADC121S051)

- +0.15, -0.11 LSB (ADC101S051

- +0.06, -0.045 LSB (ADC081S051)

- Signal-to-Noise Ratio (SNR):

- 72.0 dB (ADC121S051)

- 61.6 dB (ADC101S051)

- 49.6 dB (ADC081S051)

The ADC081S051, ADC101S051, and ADC121S051 are ideal for use in applications including portable systems, remote data acquisitions, and instrumentation and control systems. These low power ADCs are offered in LLP-6 and SOT23-6 packaging.

For FREE samples, datasheets, and more, visit www.national.com/pf/DC/ADC081S051.html www.national.com/pf/DC/ADC101S051.html www.national.com/pf/DC/ADC121S051.html

# Amplifier Closed-Loop Bandwidth Considerations in High Resolution A/D Converter Applications

converters is usually expressed in terms of the Least Significant Bit (LSB). Ideally, all error sources should be well below this level. An LSB of an ADC is defined as the finest resolution of which the ADC is capable. Quantitatively this is equal to the full scale voltage divided by the resolution of the ADC ( $V_{FS}/2^{\rm N}$ ) for one LSB, were N is the number of bits. Thus for an 8-bit converter, the error would be  $V_{FS}/256$ . If  $^{\rm I}/_{\rm 2}$  LSB is set as the required system accuracy, the acceptable accuracy limit would be:

Accuracy ( $\delta$ ) = 100% - gain error (%),

where gain error =  $1/2 (1/2^{N}) *100\%$ , Equation 3

which gives  $\delta = 100\% - 1/2 (1/2^{\text{N}}) *100\%$ , or 99.8%

The accuracy is calculated based on the -3 dB cut-off frequency at a particular close-loop gain. Approximating the frequency response of an op amp to that of a single pole filter, we get the frequency vs gain curve of such a system as shown in *Figure 1*.

Because the curve is normalized to 1 for a frequency  $f_U$  (-3 dB at unity gain), the expression for this curve, for any **f**, from *Equation 1* is

$$\mathbf{A}_{CL} = \frac{1}{\sqrt{1 + (\mathbf{f})^2}}$$

Equation 4

Solving for f gives

$$f = \sqrt{\frac{1}{(A_{CL})^2} - 1}$$

Equation 5

The question is now, for any ACL, what is the maximum signal frequency that does not exceed the specified error? From *Equation 1, Equation 3*, and *Equation 5*, and the example for 8-bit accuracy, the normalized frequency,  $f_{MAX}$ , for an amplifier requiring 99.8% accuracy, is the frequency where the gain roll off is less than  $^{1}/_{2}$  LSB is expressed as

$$f_{max} = \sqrt{\frac{1}{(0.998)^2} - 1} \times f_U = 0.062 \times f_U$$

Equation 6

for the case of unity gain.

Thus, the maximum frequency at which it is still possible to get at least 99.8% (1/2 LSB) accuracy in an 8-bit system, is 0.062 of the op amp's -3 dB frequency. In the case of the LMP2011 example, the available bandwidth for 99.8% accuracy is

$$0.062 \text{ x f}_{-3 \text{ dB}} \text{ kHz} = 0.062 \text{ x } 300 \text{ kHz} = 18.6 \text{ kHz}$$

In general, the normalized f<sub>MAX</sub> for <sup>1</sup>/<sub>2</sub> LSB error for ADCs of various resolutions can be calculated as

Normalized

$$f_{MAX} = \sqrt{\frac{1}{\left(1 - \frac{1}{2^{n-1}}\right)^2} - 1}$$

Equation 7

Using this equation, a list of normalized bandwidths for system resolutions up to 16 bits have been calculated (*Table 1*).

| System Resolution | Normalized Bandwidth |

|-------------------|----------------------|

| 8-bit             | 0.062592             |

| 9-bit             | 0.044227             |

| 10-bit            | 0.031261             |

| 11-bit            | 0.022101             |

| 12-bit            | 0.015626             |